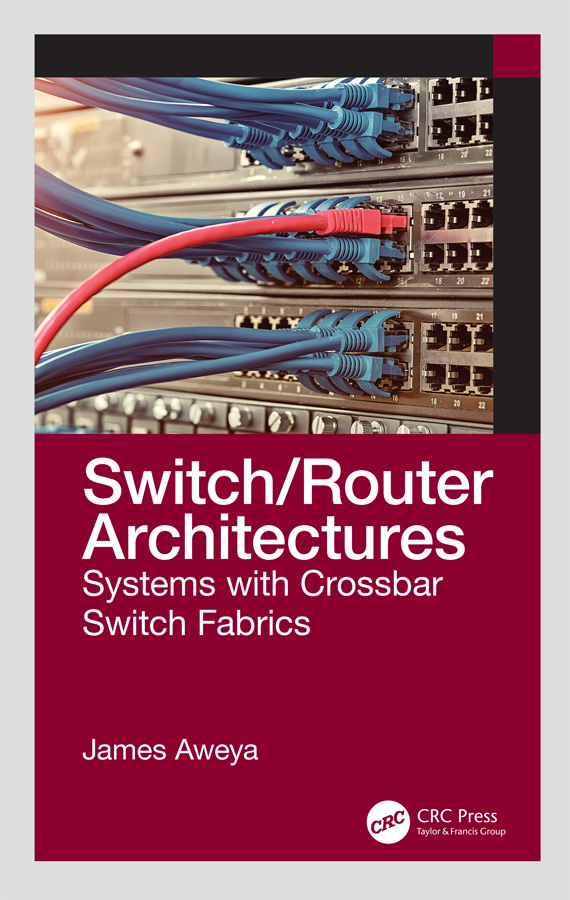

Switch/Router Architectures

Switch/Router Architectures

Systems with Crossbar Switch Fabrics

James Aweya

CRC Press

Taylor & Francis Group

6000 Broken Sound Parkway NW, Suite 300

Boca Raton, FL 33487-2742

2020 by Taylor & Francis Group, LLC

CRC Press is an imprint of Taylor & Francis Group, an Informa business

International Standard Book Number-13: 978-0-367-40785-8 (Hardback)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

Trademark Notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at

www.taylorandfrancis.com

and the CRC Press Web site at

www.crcpress.com

Contents

The continuous growth of the Internet is still creating increasing demands for bandwidth and new services from service providers networks. The growing reliance on the Internet has also created the demand for value-added services that require faster connectivity, higher quality of service, and more advanced mobile user services. There is little doubt that the rising demand for Internet connectivity and new services will continue to task the performance of network infrastructures and the individual network devices that make those networks. Networks are also under pressure to deliver these advanced services cost-effectively and at reduced operational costs.

Switches, switch/routers, routers, and network devices, in general, have traditionally been based on the following basic interconnect architectures: shared bus, shared memory, ring fabric (using point-to-point interconnects), and the crossbar switch. Shared-bus architectures are simple in design and are easy to implement. They can be constructed from readily available standard commercial products. However, despite these advantages, designers have discovered over the years that shared-bus architectures have practical performance, scalability, and fault tolerance limitations. On the issue of signal integrity, the bus architecture has practical limits on the operating frequency that can be supported, signal propagation delays (or path lengths) that are tolerable, and electrical loading on the signal lines.

The shared bus has serious bus bandwidth utilization limitation because it allows only one data transfer on the bus at a time. On the shared-bus fabric, only one transmission (time-slot) can be carried/propagated on the bus at any given time, which can result in limited throughput, scalability, and low number of network interfaces supported. Although multiple buses can be used to increase the throughput and improve the reliability of bus-based architectures, its inability to scale cost-effectively with higher data rates, number of network interfaces, and bus clock speeds is a serious limitation.

The main disadvantage of a shared-memory architecture is that bandwidth scalability is limited by the memory access speed (bandwidth). The access speeds of memories have a physical limit, and this limit prevents the shared-memory switch architecture from scaling to very high bandwidths and port speeds. Another factor is that the shared-memory bandwidth has to be at least two times the aggregate system port speeds for all the ports to run at full line rate.

Ring architectures overcome the one-at-a-time data-transfer limitations of the shared bus by allowing multiple concurrent data transfers on the ring in order to achieve higher aggregate data throughput. However, high data transfer latencies and ring reliability issues such as single points of failure are major concerns in ring architectures. The ring is susceptible to single-point-of-failures because it supports only one path between any two adjacent nodes. One malfunctioning node or link on the ring can disrupt communication on the entire fabric. The capacity of the ring architectures can be improved by implementing multiple parallel rings. These rings are usually controlled in a distributed manner, but Medium Access Control (MAC) implementation on the multiple rings can be difficult to realize.

Given the limitations of the other interconnect architectures, designers have long considered the use of crossbar switch fabrics, especially for high-performance, high-capacity systems. Crossbar switch fabrics offer several design benefits over the traditional shared-media fabrics. High-performance crossbar switches can support multiple data transfers over the fabric at the same time and can easily be made nonblocking, avoiding the bandwidth limitations seen in the shared-media fabrics with one-at-a-time data transfer type of operations.

Crossbar switch fabrics have the flexibility of connecting any input to any output, allowing for multiple concurrent data transfers. They can be designed to have relatively higher bandwidth, scalability, and fault tolerance. In addition to its basic architectural advantages, the crossbar switch can be implemented in ASICs and FPGAs. Bigger switches can be constructed from smaller crossbar switch chips. There is an abundance of literature from the commercial sector and academia on how to design crossbar switch fabrics of different types and capabilities. For this reason, a comprehensive list of references will be nearly impossible in this book. More so, crossbar switch fabric design has been a very well-studied area, especially during the days of Asynchronous Transfer Mode (ATM) switch development.

This book discusses the various switch/router architectures that use crossbar switch fabric as their internal interconnects. The book also discusses the main issues involved in the design of these switch/routers that use crossbar switch fabrics. The issues discussed include performance, implementation complexity, and scalability to higher speeds. To enhance reader understanding of switch/routers, the book begins by describing the basics of switch/routers and then the most common crossbar switch fabric-based architectures in todays networks.

![Sagar Ganatra [Sagar Ganatra] - React Router Quick Start Guide: Routing in React Applications Made Easy](/uploads/posts/book/119450/thumbs/sagar-ganatra-sagar-ganatra-react-router-quick.jpg)