Computer

Architecture

Tutorial

Using an FPGA

ARM & Verilog Introductions

Robert Dunne

Computer Architecture Tutorial Using an FPGA:

ARM & Verilog Introductions

Copyright 2020 by Robert Dunne.

All rights reserved. No part of this book may be reproduced or transmitted in any form or by any means without the prior written permission of the copyright owner and publisher. Published in the United States of America by Gaul Communications, Downers Grove, Illinois.

Cover Design: Daniel van Loon

ISBN 978-0-970112477 (hardcover, color)

ISBN 978-0-970112484 (paperback, b&w)

ISBN 978-0-970112491 (digital)

Computer Architecture Tutorial Using an FPGA: ARM & Verilog Introductions is an independent publication and has not been authorized, sponsored, or endorsed by any of the hardware or software rights holders described herein.

This book refers to the GNU software and Linux kernel. See the GNU General Public License for details which is available from the Free Software Foundation, Inc., Boston, Massachusetts.

The publisher makes no warranty, express or implied, with respect to the material contained herein. The program listings, hardware descriptions, examples, and other information presented in this book are distributed on an as is basis, without warranty. Although every precaution has been taken in the preparation of this book, neither the author nor Gaul Communications shall have any liability regarding its use.

Please send any error corrections to the author at BooksRobertDunne@gmail.com. Thank you.

18 17 16 15 14 13 12 11 10 9 8 7

Contents

Introduction

W hen Bob Dylan sang his song The Times They Are a-Changin in the mid 1960s, he was not referring to computer architecture, but to political and social change. From a programmers perspective, todays popular computer hardware architectures have barely changed from those popular in the 1960s. By no means am I saying there have been no advances in electronics and fabrication. During the past six decades, processor speeds have increased by an incredible factor of about 4,000, and computer hardware prices and physical sizes have plummeted by even a greater factor. However, todays popular X86 and ARM Central Processing Units (CPU) have very similar architectures to those of the IBM 360 and Control Data 6600 mainframes of the 1960s.

Computer Architecture Tutorial Using an FPGA: ARM & Verilog Introductions presents computer building blocks, and how they are connected to form a computing system. Registers, instruction sets, word size, memory configuration, addressing modes, and data types are factors contributing to a computers architecture. The Verilog Hardware Description Language (HDL) is a tool that can be used to describe digital electronics components and test their interconnections as they are formed into a computing system.

By working through the examples in this book and experimenting with the building blocks, the reader will receive a hands on introduction to the following:

- Computer Architecture in general

- The ARM CPU in particular

- The Verilog Hardware Description Language

- Field Programmable Gate Arrays

- Digital circuits such as decoders and multiplexers

- Assembly language programming

FPGA Use is On the Rise

Today, the times really are a-Changin in both computer architecture and education. Field Programmable Gate Arrays (FPGA) and their cousins, the Complex Programmable Logical Devices (CPLD), provide flexible digital electronics platforms that can be configured as a CPU, neural net, and almost any other digital circuit. They are the digital equivalent of the shape-shifter in science fiction. At one time, these devices were used only at national laboratories and in specialized embedded systems applications. Now, they are used by Internet search engines, the stock market, graphics applications, neural nets, every cell phone, and many other applications.

Hands On Training at Home

For over fifteen years, Ive taught digital electronics and embedded systems in the traditional college environment of lectures accompanied by supervised hands-on labs. However, much of todays education is transitioning into on-line learning with students working at home. This tutorial has been written for students and computer enthusiasts to obtain a working knowledge of computer architecture and get practical experience using FPGAs while studying at home.

The topics begin with a graphical description of the operation of individual logic gates. More complex structures like buses and decoders are then constructed and demonstrated. The Verilog coding begins with simple circuits and culminates with the assembly and execution of many ARM machine code programs. Over 150 illustrations accompany detailed descriptions for setting up the FPGA and walking through each of the nearly 100 Verilog examples.

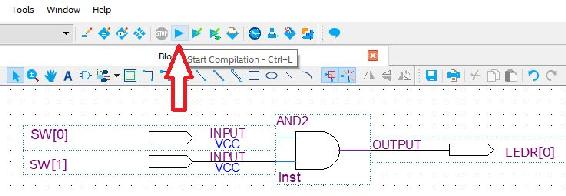

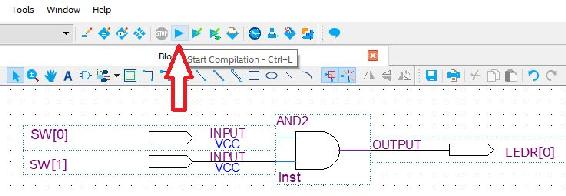

Copy of Figure 1.17: Examine operation of a single AND gate

Copy of Figure 2.7: Graphical example demonstrating digital circuits

In this tutorial, a working model of a 32-bit ARM processor is gradually built from basic principals of computer architecture. The Verilog code not only compiles ARM assembly language into 100% ARM machine code, but also executes the programs that are written. The CPU instructions are described in detail, along with examples demonstrating their operation. This CPU imitation can be run at full speed, stepped through with break points, or paused within the fetch, decode, and execute cycle.

Copy of Figure 12.11: Assembly language is presented beginning in Chapter 9

| 785. | // |

|

| 794. | // | FactN: Function that calculates factorials, N! = FactN (N). |

| 795. | // | Input: | R2: Value of N. Range = [1, 12] |

| 796. | // | LR: Return address |

| 797. | // | SP: Stack must have at least 120 bytes available |

| 798. | // | Output: | R2: Calculated value of N. Range = [1, 479001600] |

| 799. | // | R1: Used as scratch, i.e., not saved |

| 800. |

| 801. | FactN | = | IP; | // Function FactN entry address |

| 802. | `CMP | R2, 1 | `_3 // 5: Test for special, 1! = 1 |

| 803. | `BX`EQ | LR | `_3 // 6: Return with factorial in R2 |

| 804. | `PUSH | R2 | `_2 // 7: Save the input value of N |

| 805. | `PUSH | LR | `_2 // 8: Save return address |

| 806. | `SUB | R2, 1 | `_3 // 9: Prepare argument of (N-1) |

| 807. | `BL | FactN | `_2 // A: Get value for (N-1)! in R2 |

| 808. | `POP | LR | `_2 // B: Reload return address |

|